Hal init Flow 분석

Hal init 과정을 분석해 보았다. HAL init 시 아래와 같은 함수를 호출 한다.

/* Reset of all peripherals, Initializes the Flash interface and the Systick. */

HAL_Init();

HAL_Init 함수는 아래와 같이 정의 되어 있다.

HAL_StatusTypeDef HAL_Init(void)

{

/* Configure Flash prefetch */

#if (PREFETCH_ENABLE != 0)

#if defined(STM32F101x6) || defined(STM32F101xB) || defined(STM32F101xE) || defined(STM32F101xG) || \

defined(STM32F102x6) || defined(STM32F102xB) || \

defined(STM32F103x6) || defined(STM32F103xB) || defined(STM32F103xE) || defined(STM32F103xG) || \

defined(STM32F105xC) || defined(STM32F107xC)

/* Prefetch buffer is not available on value line devices */

__HAL_FLASH_PREFETCH_BUFFER_ENABLE();

#endif

#endif /* PREFETCH_ENABLE */

/* Set Interrupt Group Priority */

HAL_NVIC_SetPriorityGrouping(NVIC_PRIORITYGROUP_4);

/* Use systick as time base source and configure 1ms tick (default clock after Reset is HSI) */

HAL_InitTick(TICK_INT_PRIORITY);

/* Init the low level hardware */

HAL_MspInit();

/* Return function status */

return HAL_OK;

}

stm32f1xx_hal_conf.h

/* ########################### System Configuration ######################### */

/**

* @brief This is the HAL system configuration section

*/

#define VDD_VALUE 3300U /*!< Value of VDD in mv */

#define TICK_INT_PRIORITY 15U /*!< tick interrupt priority (lowest by default) */

#define USE_RTOS 0U

#define PREFETCH_ENABLE 1U

-mcpu=cortex-m3 -std=gnu11 -g3 -DSTM32F103xB

/**

* @brief Enable the FLASH prefetch buffer.

* @retval None

*/

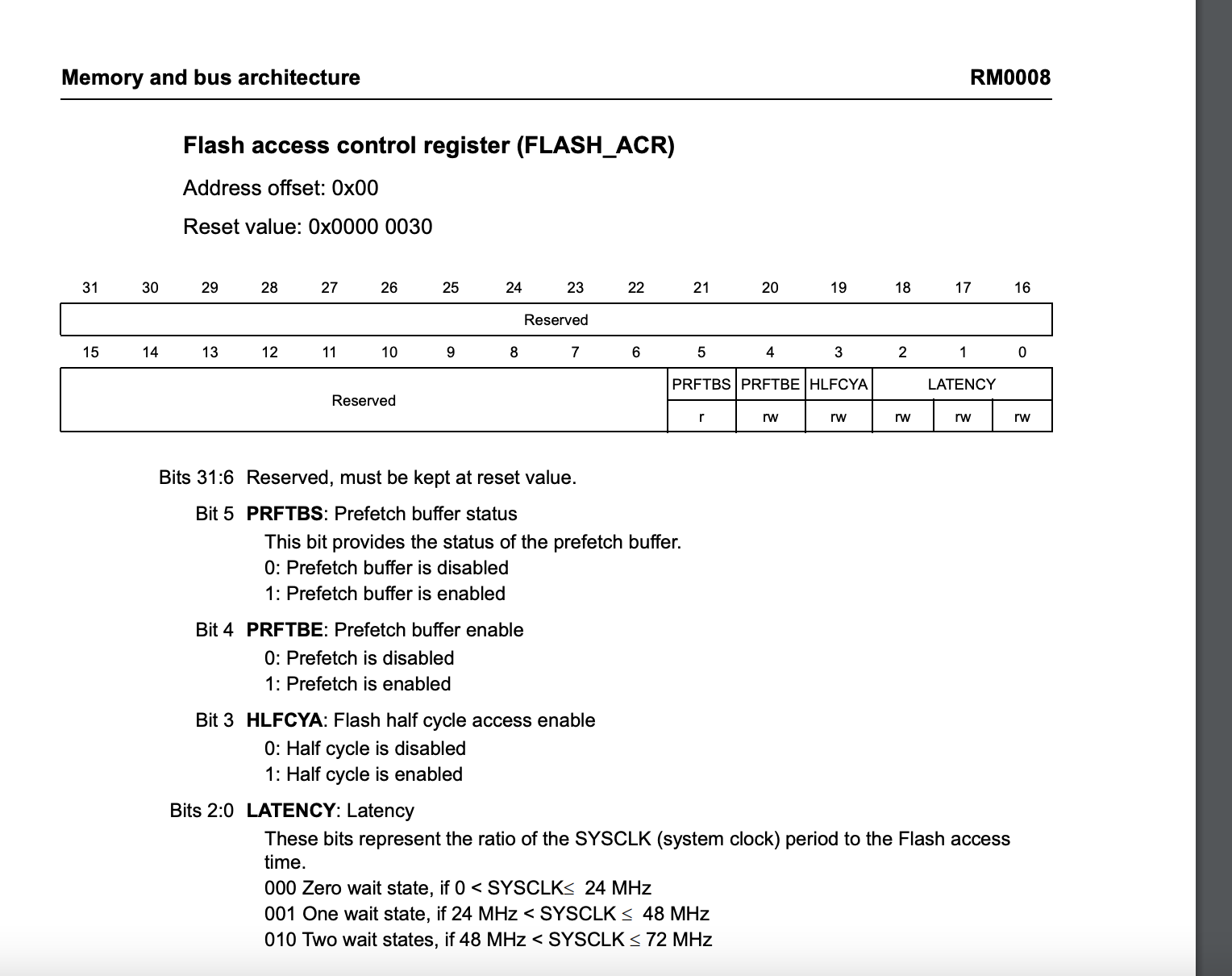

#define __HAL_FLASH_PREFETCH_BUFFER_ENABLE() (FLASH->ACR |= FLASH_ACR_PRFTBE)

#define FLASH ((FLASH_TypeDef *)FLASH_R_BASE)

/**

* @brief FLASH Registers

*/

typedef struct

{

__IO uint32_t ACR;

__IO uint32_t KEYR;

__IO uint32_t OPTKEYR;

__IO uint32_t SR;

__IO uint32_t CR;

__IO uint32_t AR;

__IO uint32_t RESERVED;

__IO uint32_t OBR;

__IO uint32_t WRPR;

} FLASH_TypeDef;

#define FLASH_R_BASE (AHBPERIPH_BASE + 0x00002000UL) /*!< Flash registers base address */

#define AHBPERIPH_BASE (PERIPH_BASE + 0x00020000UL)

#define PERIPH_BASE 0x40000000UL /*!< Peripheral base address in the alias region */

#define FLASH_ACR_PRFTBE_Pos (4U)

#define FLASH_ACR_PRFTBE_Msk (0x1UL << FLASH_ACR_PRFTBE_Pos) /*!< 0x00000010 */

#define FLASH_ACR_PRFTBE FLASH_ACR_PRFTBE_Msk /*!< Prefetch Buffer Enable */

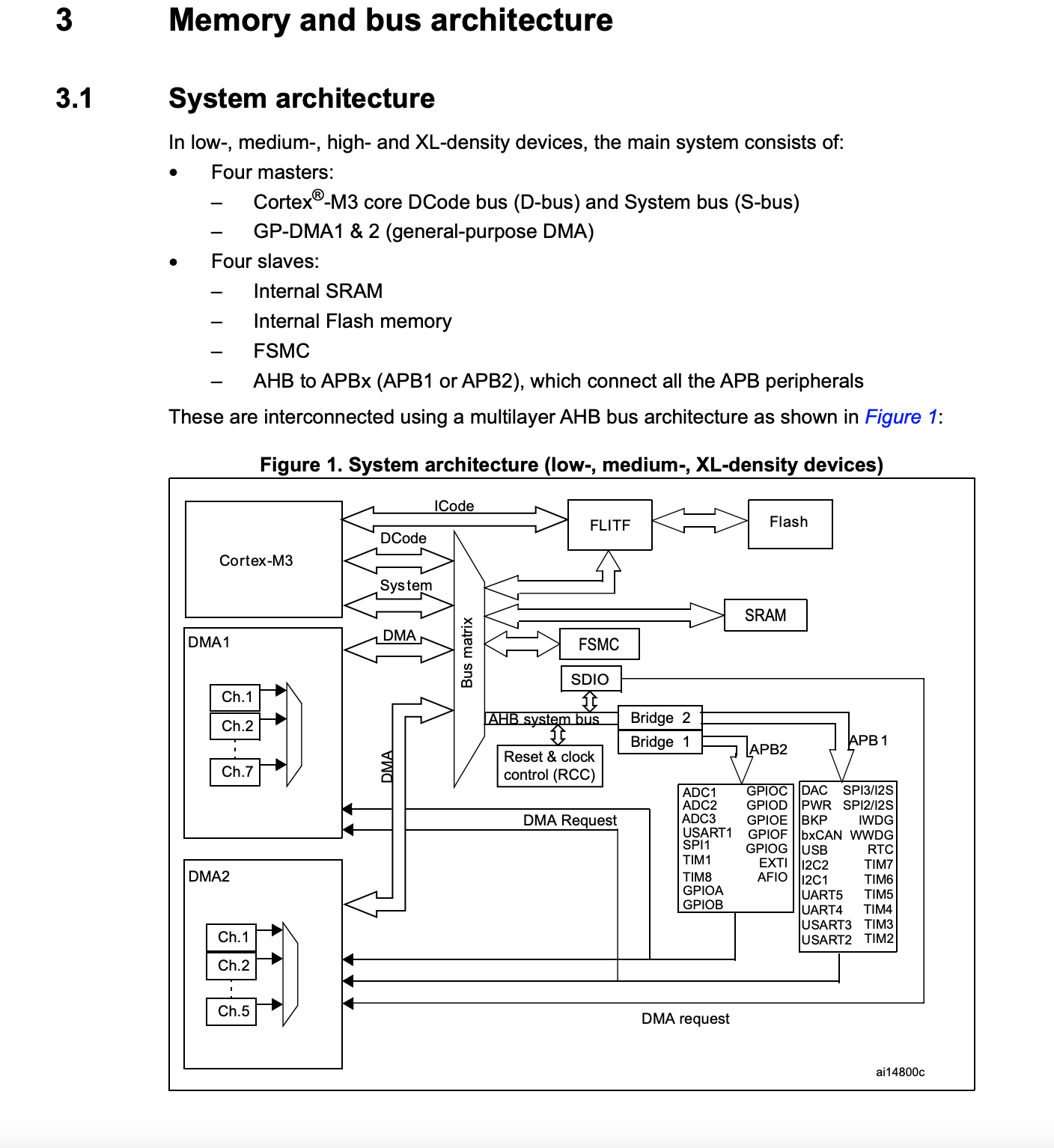

프로그램 실행 시 CPU나 Flash로 부터 명령들을 미리 저장하는 역할이 Prefetch Buffer로 생각한다.

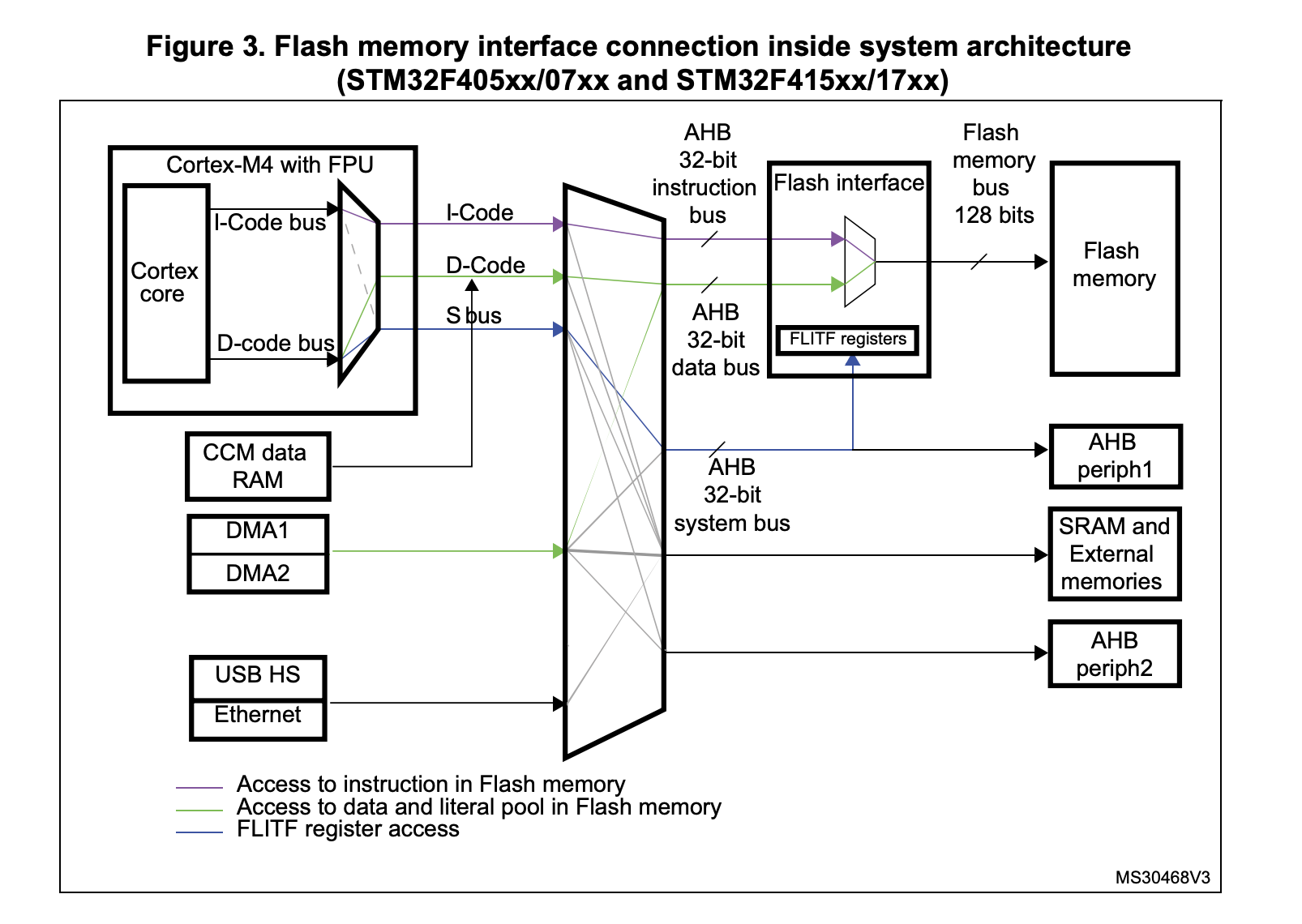

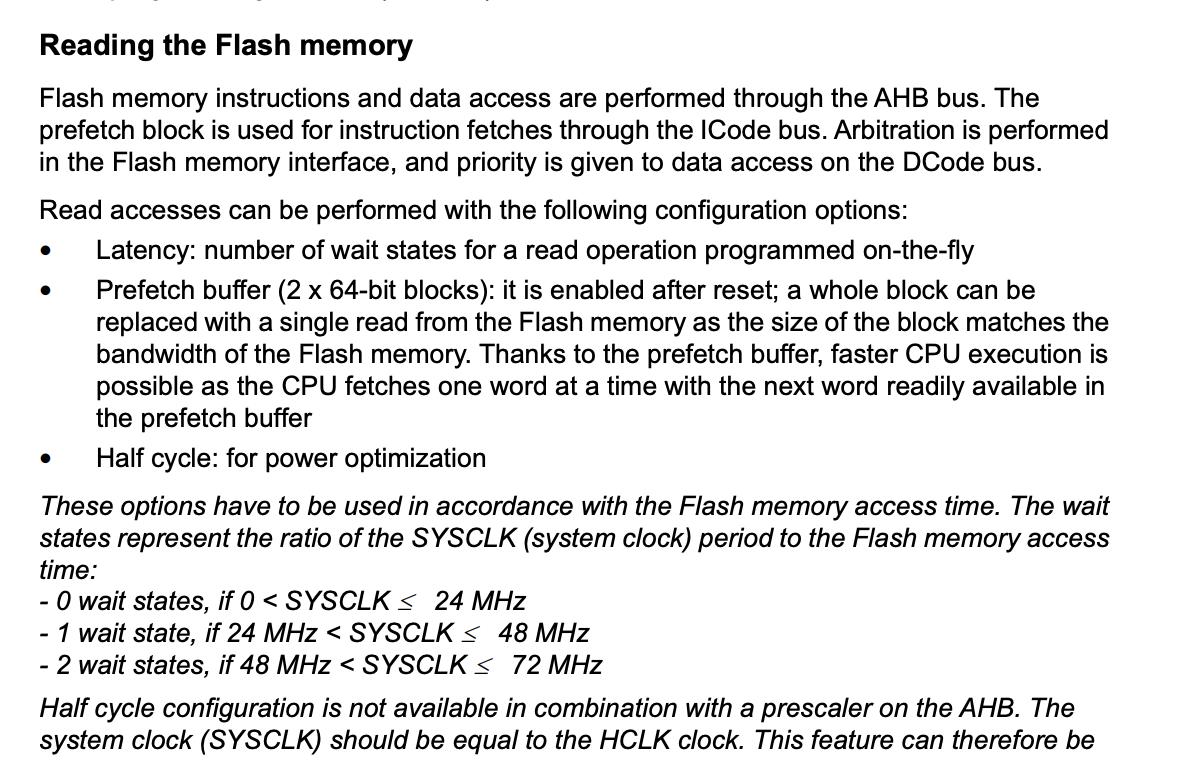

위 그림과 같이 FLITF를 통해 I-Code, D-Code가 중대 되며 D-Code의 우선순위가 높다.

I-Code bus: instruction fetch

D-Code bus: Literal pool (상수나 data)

Prefetch Buffer는 Flash Memory로 부터의 명령(Flash memory instruction(I-Code, D-code))을 미리 저장하여 CPU 실행 속도에 도움을 준다고 생각한다.

어떻게 Prefech Buffer에 명령이 저장되는 좀더 스터디가 필요하다.

참고한 링크는 아래와 같다.

http://poohyhoh.blogspot.com/2010/08/cortex-m3-stm32-flash-program-1.html

https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=thumbdown&logNo=220302169034

http://www.jkelec.co.kr/img/lecture/cortex_arch/cortex_arch_2.html

http://www.ntrexgo.com/archives/2867

https://developer.arm.com/documentation/ddi0337/e/Introduction/Prefetch-Unit